# **TL7231MD**

# FULL LAYER-III ISO/IEC 11172-3 AUDIO DECODER

- Single-chip ISO/IEC 11172-3 Layer III Audio Decoder ■

- Supports All MPEG Bit Rates Including Free Format

- Supports 32/44.1/48KHz Sampling Frequencies for MPEG Bit Stream

- Supports Single Channel, Dual Channel, Stereo, and Joint Stereo

- Any Combination of Intensity Stereo and MS Stereo is supported.

- Serial Bit Stream Input

- 8-bit Host Interface Port

- Digital Volume Control

- Digital Bass/Treble Control

- 6-Band Equalizer Function

- Voice Record/Playback Capability

- On-chip DAC with 1-bit Sigma Delta Modulation

- Supports Off-chip DAC Interface

- On-chip ADC with 12-bit Resolution

- Power Management to Reduce Power Consumption

- PLL for Internal Clocks and for Output PCM Clock Generation

- Single 16.9344MHz External Clock Input

- 3.0 V Operation

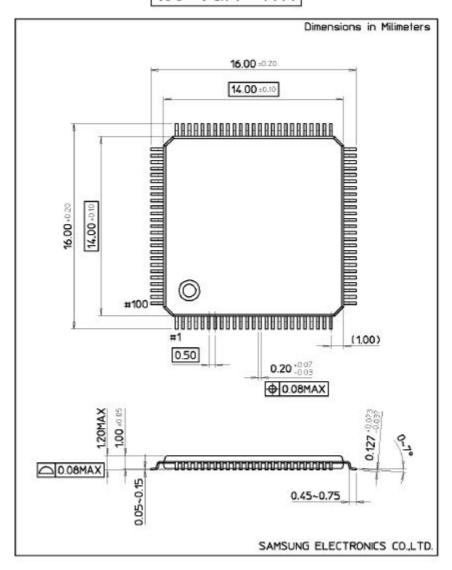

- Small Footprint 100-pin Thin Quad Flat Package

### **DESCRIPTION**

TL7231MD is a single-chip ISO/IEC 11172-3 Layer III audio decoder, capable of decoding compressed elementary bit streams as specified in ISO/IEC standard. Since it integrated on-chip ADC and on-chip DAC, it can provide you more small and cheaper solution for MP3 player application. It is designed to be well suited for portable audio appliances.

TL7231MD receives the input data bit stream through a serial data interface. The decoded signal is 16-bit serial PCM format that can be sent directly to DAC. The generated PCM data can be sent to on-chip DAC or off-chip DAC according to user preference. The off-chip DAC interface is programmable to adapt the PCM output of TL7231MD to the most common DACs used on the market.

An 8-bit host interface port is provided to receive control information from and send status information to host. 8-bit microcontrollers such as those of Intel or Motorola can be connected easily.

TL7231MD has the capability of compressing voice signals. It can receive voice signals through on-chip ADC. The compressed voice signals are transmitted to or received from host through serial data interface. It can also reproduce the voice signals from the compressed voice signals.

September 1999 1/37

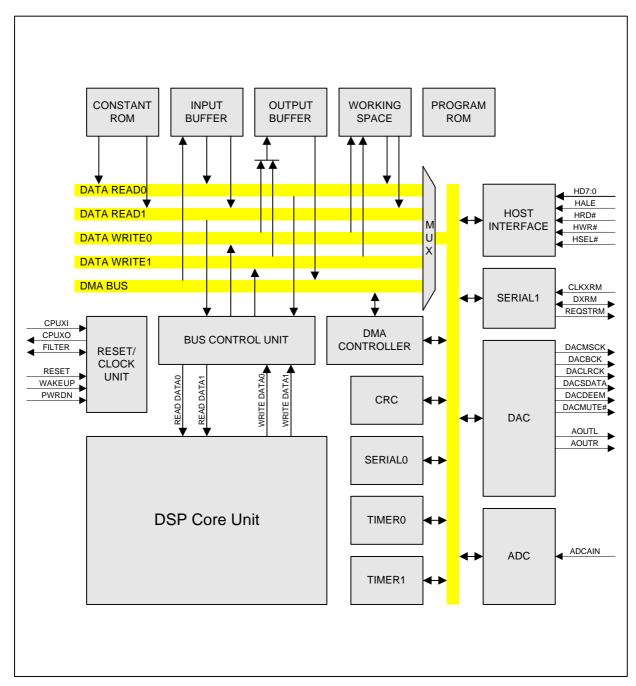

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram of TL7231MD

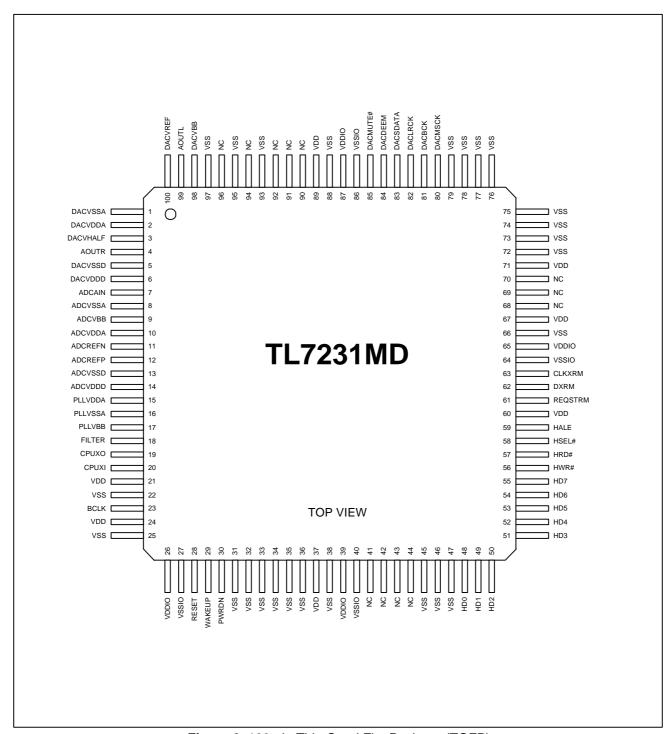

## PIN DESCRIPTION

Figure 2. 100-pin Thin Quad Flat Package (TQFP)

Table 1. Pin Locations with Pin Names

| PIN | NAME     | PIN | NAME   | PIN | NAME    | PIN | NAME     |

|-----|----------|-----|--------|-----|---------|-----|----------|

| 1   | DACVSSA  | 26  | VDDIO  | 51  | HD3     | 76  | VSS      |

| 2   | DACVDDA  | 27  | VSSIO  | 52  | HD4     | 77  | VSS      |

| 3   | DACVHALF | 28  | RESET  | 53  | HD5     | 78  | VSS      |

| 4   | AOUTR    | 29  | WAKEUP | 54  | HD6     | 79  | VSS      |

| 5   | DACVSSD  | 30  | PWRDN  | 55  | HD7     | 80  | DACMSCK  |

| 6   | DACVDDD  | 31  | VSS    | 56  | HWR#    | 81  | DACBCK   |

| 7   | ADCAIN   | 32  | VSS    | 57  | HRD#    | 82  | DACLRCK  |

| 8   | ADCVSSA  | 33  | VSS    | 58  | HSEL#   | 83  | DACSDATA |

| 9   | ADCVBB   | 34  | VSS    | 59  | HALE    | 84  | DACDEEM  |

| 10  | ADCVDDA  | 35  | VSS    | 60  | VDD     | 85  | DACMUTE# |

| 11  | ADCREFN  | 36  | VSS    | 61  | REQSTRM | 86  | VSSIO    |

| 12  | ADCREFP  | 37  | VDD    | 62  | DXRM    | 87  | VDDIO    |

| 13  | ADCVSSD  | 38  | VSS    | 63  | CLKXRM  | 88  | VSS      |

| 14  | ADCVDDD  | 39  | VDDIO  | 64  | VSSIO   | 89  | VDD      |

| 15  | PLLVDDA  | 40  | VSSIO  | 65  | VDDIO   | 90  | NC       |

| 16  | PLLVSSA  | 41  | NC     | 66  | VSS     | 91  | NC       |

| 17  | PLLVBB   | 42  | NC     | 67  | VDD     | 92  | NC       |

| 18  | FILTER   | 43  | NC     | 68  | NC      | 93  | VSS      |

| 19  | CPUXO    | 44  | NC     | 69  | NC      | 94  | NC       |

| 20  | CPUXI    | 45  | VSS    | 70  | NC      | 95  | VSS      |

| 21  | VDD      | 46  | VSS    | 71  | VDD     | 96  | NC       |

| 22  | VSS      | 47  | VSS    | 72  | VSS     | 97  | VSS      |

| 23  | BCLK     | 48  | HD0    | 73  | VSS     | 98  | DACVBB   |

| 24  | VDD      | 49  | HD1    | 74  | VSS     | 99  | AOUTL    |

| 25  | VSS      | 50  | HD2    | 75  | VSS     | 100 | DACVREF  |

Table 2. Pin Functions with Location

| NAME     | PIN | NAME    | PIN | NAME    | PIN | NAME   | PIN |

|----------|-----|---------|-----|---------|-----|--------|-----|

| ADCAIN   | 7   | DACVSSA | 1   | NC      | 92  | VSS    | 34  |

| ADCREFN  | 11  | DACVSSD | 5   | NC      | 94  | VSS    | 35  |

| ADCREFP  | 12  | DXRM    | 62  | NC      | 96  | VSS    | 36  |

| ADCVBB   | 9   | FILTER  | 18  | PLLVBB  | 17  | VSS    | 38  |

| ADCVDDA  | 10  | HD0     | 48  | PLLVDDA | 15  | VSS    | 45  |

| ADCVDDD  | 14  | HD1     | 49  | PLLVSSA | 16  | VSS    | 46  |

| ADCVSSA  | 8   | HD2     | 50  | PWRDN   | 30  | VSS    | 47  |

| ADCVSSD  | 13  | HD3     | 51  | REQSTRM | 61  | VSS    | 66  |

| AOUTL    | 99  | HD4     | 52  | RESET   | 28  | VSS    | 72  |

| AOUTR    | 4   | HD5     | 53  | VDD     | 21  | VSS    | 73  |

| BCLK     | 23  | HD6     | 54  | VDD     | 24  | VSS    | 74  |

| CLKXRM   | 63  | HD7     | 55  | VDD     | 37  | VSS    | 75  |

| CPUXI    | 20  | HALE    | 59  | VDD     | 60  | VSS    | 76  |

| CPUXO    | 19  | HRD#    | 57  | VDD     | 67  | VSS    | 77  |

| DACBCK   | 81  | HSEL#   | 58  | VDD     | 71  | VSS    | 78  |

| DACDEEM  | 84  | HWR#    | 56  | VDD     | 89  | VSS    | 79  |

| DACLRCK  | 82  | NC      | 41  | VDDIO   | 26  | VSS    | 88  |

| DACMSCK  | 80  | NC      | 42  | VDDIO   | 39  | VSS    | 93  |

| DACMUTE# | 85  | NC      | 43  | VDDIO   | 65  | VSS    | 95  |

| DACSDATA | 83  | NC      | 44  | VDDIO   | 87  | VSS    | 97  |

| DACVBB   | 98  | NC      | 68  | VSS     | 22  | VSSIO  | 27  |

| DACVDDA  | 2   | NC      | 69  | VSS     | 25  | VSSIO  | 40  |

| DACVDDD  | 6   | NC      | 70  | VSS     | 31  | VSSIO  | 64  |

| DACVHALF | 3   | NC      | 90  | VSS     | 32  | VSSIO  | 86  |

| DACVREF  | 100 | NC      | 91  | VSS     | 33  | WAKEUP | 29  |

Table 3. Pin Descriptions

| Signal Name | Туре  | Description                                                                                        |

|-------------|-------|----------------------------------------------------------------------------------------------------|

| Signal Name | i ype | · · ·                                                                                              |

| ODI IVI     |       | Internal PLL Interface                                                                             |

| CPUXI       | 1     | CPU Clock In. 16.9344MHz crystal clock input.                                                      |

| CPUXO       | 0     | CPU Clock Out. 16.9344MHz crystal clock output.                                                    |

| FILTER      | 0     | Charge Pump Out. External capacitor should be connected                                            |

|             |       | between this pin and analog ground.                                                                |

| 2011        |       | Clock Signal                                                                                       |

| BCLK        | 0     | Processor Clock Output.                                                                            |

|             |       | Reset & Power Down Control                                                                         |

| RESET       | ı     | Chip Reset. Reset input to the chip. Internal pull down.                                           |

|             |       | Wake Up. When high, chip is waked up from SLEEP state. This pin                                    |

| WAKEUP      | I     | should be remained active at least 1 clock cycle and inactive before                               |

|             |       | the host issues next SLEEP command. Internal pull down.                                            |

|             |       | Power Down. This pin controls PWRDOWN state. When high, chip                                       |

|             |       | goes to very low power consumption state. After deactivation,                                      |

| PWRDN       | I     | WAKEUP pin should be remained low at least 150μs. Internal pull                                    |

|             |       | down.                                                                                              |

|             |       | (Restriction: This pin should be active ONLY in SLEEP state.                                       |

|             |       | Otherwise, Chip reset should be activated.)                                                        |

|             |       | MCU Serial Interface                                                                               |

| CLKXRM      | l     | Serial Clock. MCU serial interface clock.                                                          |

|             |       | Serial Data. When MCU transmits data, this data pin is sampled at                                  |

| DVDM        | 1/0   | negative edge of CLKXRM. When MCU receives data, Data is valid                                     |

| DXRM        | I/O   | from negative edge of CLKXRM to next negative edge of CLKXRM.                                      |

|             |       | DXRM should be sampled at positive edge of CLKXRM. After reset,                                    |

|             |       | TL7231MD is set to transmit the most significant bit first.                                        |

| REQSTRM     | 0     | Request Bit Stream Data. MCU must check this pin to determine to                                   |

| REQUIRIN    | 0     | continue receiving or transmitting. MCU should transmit or receive data during this signal active. |

|             |       |                                                                                                    |

|             |       | MCU HIP(Host Interface Port) Interface                                                             |

| HSEL#       | l     | HIP Enable. When Low, HIP is selected.                                                             |

| HALE        | ı     | HIP Address Latch Enable. When High, HD[7:0] should have HIP                                       |

|             |       | address, which is sampled at negative edge of this signal.                                         |

| HRD#        | I     | HIP Read Enable. When low, data is loaded to HD[7:0], which                                        |

|             |       | should be sampled at positive edge of this signal.                                                 |

| HWR#        | I     | <b>HIP Write Enable.</b> Data at HD[7:0] is sampled at positive edge of this signal.               |

| HD[7:0]     | I/O   | HIP Address/Data Bus. Multiplexed address lines and data lines.                                    |

| []          | ., 0  | Internal ADC Interface                                                                             |

|             |       | ADC Analog Input. Analog input spans between ADCREFP and                                           |

| ADCAIN      | I     | ADCREFN.                                                                                           |

| 4000555     |       | ADC Internal Reference Top Bias. Connect this pin to voltage                                       |

| ADCREFP     | I     | between ADCVDDA and 2.0V.                                                                          |

| ADCREFN     | I     | ADC Internal Reference Bottom Bias. Connect this pin to ground.                                    |

| PWR   | ADC Supply Voltage for Analog Circuit. Connect this pin to the +3.0V supply voltage.         |

|-------|----------------------------------------------------------------------------------------------|

| GND   | ADC Ground for Analog Circuit. Connect this pin to ground.                                   |

| PWR   | ADC Supply Voltage for Digital Circuit. Connect this pin to the +3.0V supply voltage.        |

| GND   | ADC Ground for Digital Circuit. Connect this pin to ground.                                  |

| GND   | ADC Analog/Digital Bulk Bias. Connect this pin to ground.                                    |

|       | External DAC Interface                                                                       |

| 0     | DAC Master Clock. 384×Fs clock.                                                              |

| 0     | DAC Bit Clock. 32×Fs clock.                                                                  |

| 0     | DAC Sample Rate Clock. Fs clock.                                                             |

| 0     | DAC Serial Data. Serial data.                                                                |

| 0     | DAC Deemphasis. When deemphasis is on, this signal is high. It                               |

| )     | can be set/clear through HIP commands.                                                       |

| 0     | <b>DAC Mute.</b> Analog output mute. When external DAC is set to mute                        |

| U     | on, this signal is low. It can be set/clear through HIP commands.                            |

|       | Internal DAC Interface                                                                       |

| 0     | Analog Output for Left-Channel.                                                              |

| 0     | Analog Output for Right-Channel.                                                             |

| I/O   | DAC Reference Voltage Output for Bypass.                                                     |

| I/O   | DAC Reference Voltage Output for Bypass.                                                     |

| PWR   | <b>DAC Supply Voltage for Analog Circuit.</b> Connect this pin to the +3.0V supply voltage.  |

| GND   | DAC Ground for Analog Circuit. Connect this pin to ground.                                   |

| PWR   | <b>DAC Supply Voltage for Digital Circuit.</b> Connect this pin to the +3.0V supply voltage. |

| GND   | DAC Ground for Digital Circuit. Connect this pin to ground.                                  |

| GND   | DAC Pad Bulk Bias. Connect this pin to ground.                                               |

|       | Power/Ground Pins                                                                            |

| PWR   | Supply Voltage. Connect this pin to the +3.0V supply voltage.                                |

| GND   | Circuit Ground. Connect this pin to ground.                                                  |

| D\\/D | Supply Voltage for I/O Buffers. Connect this pin to the +3.0V                                |

| LAAL  | supply voltage.                                                                              |

| GND   | Circuit Ground for I/O Buffers. Connect this pin to ground.                                  |

|       | GND PWR GND O O O O O O O I/O I/O I/O PWR GND GND PWR GND GND PWR GND GND PWR                |

## **FUNCTIONAL DESCRIPTION**

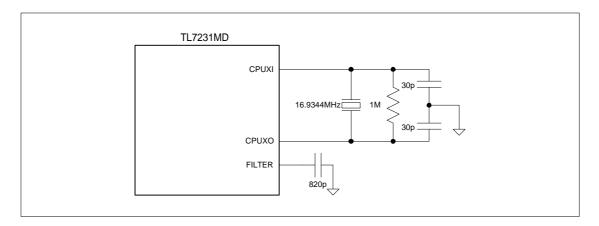

### **RESET/CLOCK UNIT**

TL7231MD is driven by a single clock at the frequency of 16.9344MHz. The clock is derived from an external source or from an industry standard crystal oscillator, generating input frequency of 16.9344MHz. The clock generation unit has a PLL, and all the internal clock signals including internal DAC/ADC clocks are generated with the input clock.

When TL7231MD is in power-on-reset, RESET signal should be active at least  $150\mu s$  till the internal PLL is stabilized. To reset TL7231MD during normal operation, RESET signal should be active at least 16 cycles.

Figure 3. Clock Circuit

### **DSP CORE LOGIC**

The core logic of TL7231MD is a 32-bit floating-point DSP processor. The independent multiplier and accumulator of TL7231MD can achieve high performance. Internal registers are 40-bit registers that store values with a 32-bit mantissa and an 8-bit exponent. These registers can serve as both the source and destination for any arithmetic operation. Since all the data input/output transactions are managed by DMA, there is no computational overhead due to data transactions.

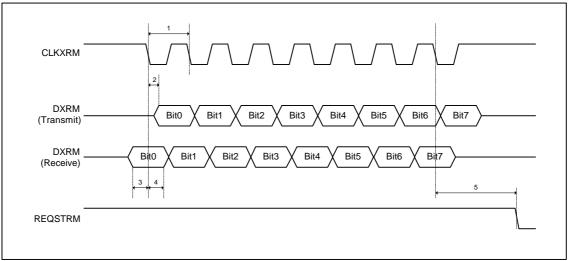

### SERIAL INTERFACE

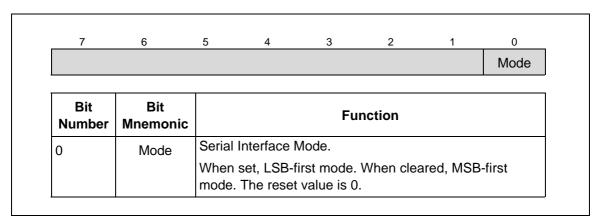

The serial interface of TL7231MD is used to receive MPEG bit stream data or transmit/receive voice data. It is configured to transfer 8 bits of data per word. It can be configured to be LSB-first or MSB first transfer mode. LSB-first means that the data bits are transmitted and received least-significant bit (LSB) first. MSB-first means that the data bits are transmitted and received most-significant bit (MSB) first. The clock for the serial interface should be generated externally.

The related signals are CLKXRM, DXRM, and REQSTRM. REQSTRM is used for synchronization between microcontroller and TL7231MD, and data is transferred during REQSTRM active.

When microcontroller tries to send data to TL7231MD, it should check whether REQSTRM is active or not. If the signal is active, microcontroller sets its serial interface to transmit mode and send serial clock and serial data. After transmitting each byte, microcontroller should check REQSTRM to decide whether next byte is to be transmitted or not.

When microcontroller tries to receive data from TL7231MD, it should check whether REQSTRM is active or not. If the signal is active, microcontroller sets its serial interface to receive mode and send serial clock and receive serial data from TL7231MD. After receiving each byte, microcontroller should check REQSTRM to decide whether TL7231MD will transmit next byte or not.

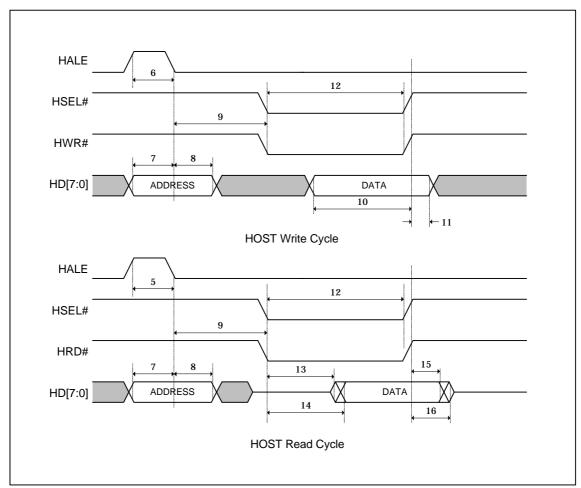

## **HOST INTERFACE PORT (HIP)**

Host interface port is used to send commands to and receive status information from TL7231MD. HIP of TL7231MD is a parallel I/O port that makes a connection to a host processor easily. Through the HIP, TL7231MD can be used as a memory-mapped peripheral to a host processor. The HIP can be thought of as an area of dual-port memory that allows communication between the computational core of the TL7231MD and host. The HIP is completely asynchronous. The host processor can write data into the HIP while the TL7231MD is operating at full speed. HIP transfers are managed using interrupt scheme.

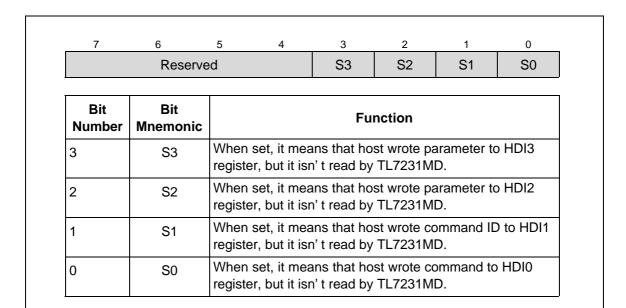

HIP contains 21 registers. Four of them are data-in registers (HDI0/HDI1/HDI2/HDI3) and one of them is a status register (HSR4). The remaining 16 registers are data-out registers (HDO0/./HDO15). Data written into HDIs by host are read by TL7231MD. Through these registers host can give necessary commands to TL7231MD. A command is written into a HDI0, and the required parameters of the command are written into the HDI1/HDI2/HDI3. The status register (HSR4) keeps the information whether data written into the data-in registers are read by TL7231MD. The status register is managed automatically by TL7231MD and can be read by host. TL7231MD starts HIP command processing when HDI0 register is written. So if any command requires parameters, user should write parameters first, and then write command.

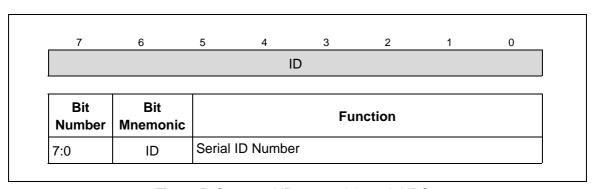

Serial ID number can be used to check whether given command has been accepted or not. TL7231MD can receive the serial ID value through HDO0 when TL7231MD has accepted the given command. Thus when commands are given to TL7231MD with different serial ID numbers, it can be examined which command is being processed. Serial ID number itself hasn't any special meaning. If this feature is not needed, it is not required to send ID values with commands. Then the value of HDO0 is undetermined. There is an exception for the ID number convention. If you use HIP command 0Dh(Revision Code), TL7231MD returns the TL7231MD revision number, not the ID number.

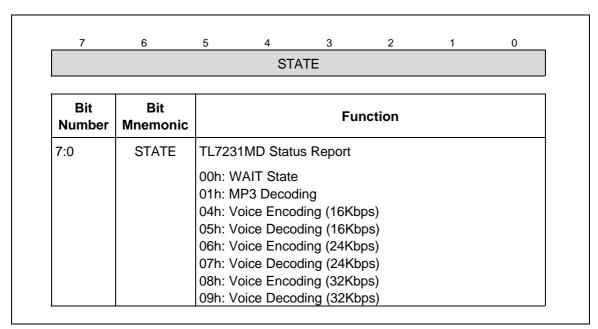

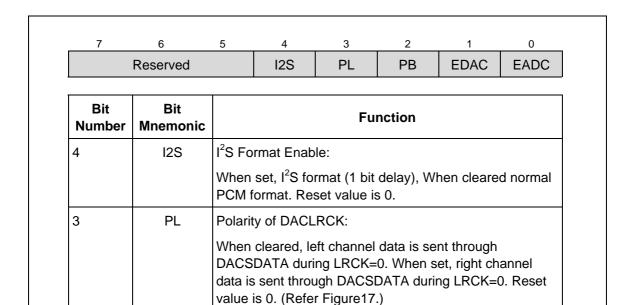

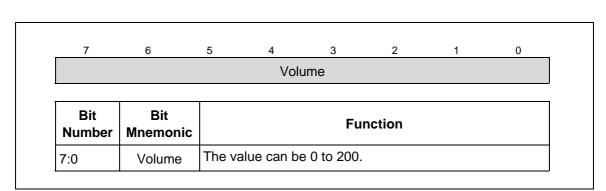

HDOs are written by TL7231MD and can be read by host. All HIP registers should be memory-mapped into the memory space of the host processor. The address space of those registers is shown in Table 4. The usable commands are listed in Table 6. The contents reported by HDOs are shown from Figure 4 to Figure 16.

Table 4. Address of Host Interface Port Registers

| ADDRESS   | REGISTERS    | DESCRIPTION                                                                                             |

|-----------|--------------|---------------------------------------------------------------------------------------------------------|

| 0h        | HDI0         | Command                                                                                                 |

| 1h        | HDI1         | Serial ID Number                                                                                        |

| 2h ~ 3h   | HDI2/HDI3    | Parameters if needed                                                                                    |

| 4h        | HSR4         | Status Register (Fig. 4)                                                                                |

| 10h       | HDO0         | Command Serial ID Number (Fig. 5)                                                                       |

| 11h       | HDO1         | Decoder State (Fig. 6)                                                                                  |

| 12h       | HDO2         | IO Status (Fig.7)                                                                                       |

| 13h       | HDO3         | IO Status (Fig. 8)                                                                                      |

| 14h       | HDO4         | Volume (Fig. 9)                                                                                         |

| 15h       | HDO5         | Serial Interface Mode (Fig. 10)                                                                         |

| 16h ~ 1Fh | HDO6 ~ HDO15 | The information provided by these registers depends on the mode setting of TL7231MD. (Refer to Table 5) |

The information provided by HDO6 to HDO15 depends on the mode setting of TL7231MD. Refer to Table 5. The mode can be set by using HIP command 19h(Report Format). For this command, refer to Table 6.

Table 5. The contents of HDO6 ~ HDO15 according to mode setting

| ADDRESS | REGISTERS | DESCRIPTION                                                                                                                                                                                                                                                                                        |

|---------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16h     | HDO6      | Mode0: 00h Mode1: Tone Control Status. When tone control is enabled, 1 is reported. Otherwise, 0 is reported. Mode2: MP3 Frame Count (Fig. 11) Mode3: Voice Data Code Count (Fig. 11) Mode4: Equalizer Control Status. When equalizer control is enabled, 1 is reported. Otherwise, 0 is reported. |

| 17h     | HDO7      | Mode0: 00h Mode1: Tone Control - Prescaling Information Mode2: MP3 Frame Count (Fig. 11) Mode3: Voice Data Code Count (Fig. 11) Mode4: EQ Control – Prescaling Information                                                                                                                         |

| 18h     | HDO8      | Mode0: 00h Mode1: Tone Control – Bass Cutoff Frequency Mode2: MP3 Frame Count (Fig. 11) Mode3: Voice Data Code Count (Fig. 11) Mode4: EQ Control – Band1 Gain                                                                                                                                      |

| 19h     | HDO9      | Mode0: 00h Mode1: Tone Control – Bass Gain Mode2: MP3 Frame Count (Fig. 11) Mode3: Voice Data Code Count (Fig. 11) Mode4: EQ Control –Band2 Gain                                                                                                                                                   |

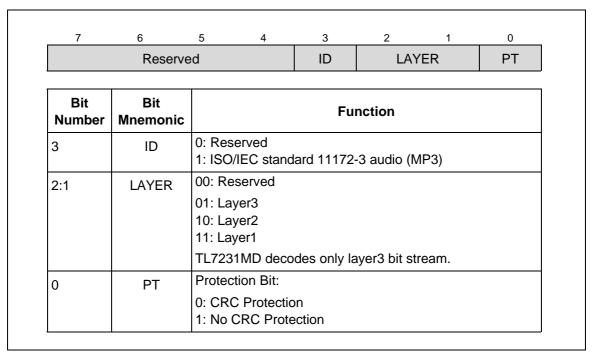

| 1Ah     | HDO10     | Mode0: 00h                                                                                                                                                                                                                                                                                         |

|     | 1     | Made 4. Taxaa Oo ataalii. Taabila Oo taff Farana      |

|-----|-------|-------------------------------------------------------|

|     |       | Mode1: Tone Control – Treble Cutoff Frequency         |

|     |       | Mode2: The most recently synchronized frame header of |

|     |       | MP3 bit stream. (Fig. 12)                             |

|     |       | Mode3: 00h                                            |

|     |       | Mode4: EQ Control – Band3 Gain                        |

| 1Bh | HDO11 | Mode0: 00h                                            |

|     |       | Mode1: Tone Control – Treble Gain                     |

|     |       | Mode2: The most recently synchronized frame header of |

|     |       | MP3 bit stream. (Fig. 13)                             |

|     |       | Mode3: 00h                                            |

|     |       | Mode4: EQ Control – Band4 Gain                        |

| 1Ch | HDO12 | Mode0: 00h                                            |

|     |       | Mode1: 00h                                            |

|     |       | Mode2: The most recently synchronized frame header of |

|     |       | MP3 bit stream. (Fig. 14)                             |

|     |       | Mode3: 00h                                            |

|     |       | Mode4: EQ Control – Band5 Gain                        |

| 1Dh | HDO13 | Mode0: 00h                                            |

|     |       | Mode1: 00h                                            |

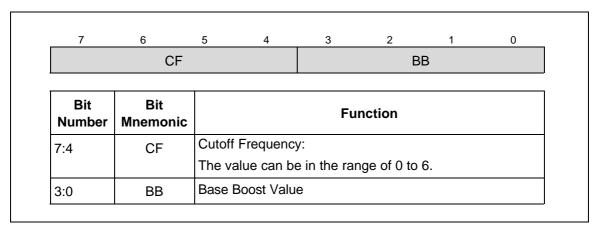

|     |       | Mode2: Bass Boost Information (Fig. 15)               |

|     |       | Mode3: 00h                                            |

|     |       | Mode4: EQ Control – Band6 Gain                        |

| 1Eh | HDO14 | Mode0: 00h                                            |

|     |       | Mode1: 00h                                            |

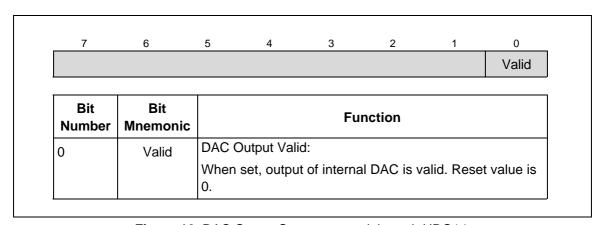

|     |       | Mode2: DAC Output Valid (Fig. 16)                     |

|     |       | Mode3: 00h                                            |

|     |       | Mode4: 00h                                            |

| 1Fh | HDO15 | Mode0: 00h                                            |

|     |       | Mode1: 00h                                            |

|     |       | Mode2: CRC Error Count                                |

|     |       | Mode3: 00h                                            |

|     |       | Mode4: 00h                                            |

|     | 1     |                                                       |

Table 6. Host Interface Port Commands

| СОММ | PARAME |                | ost Interface Port Commands                                              |

|------|--------|----------------|--------------------------------------------------------------------------|

| AND  | TER    | MEANING        | DESCRIPTION                                                              |

| 00h  | None   | Stop           | Stop execution and go into WAIT state.                                   |

| 01h  | None   | MP3 Decoding   | Execute MP3 decoding.                                                    |

| 04h  | None   | Voice Encoding | Execute voice encoding (16Kbps).                                         |

| 05h  | None   | Voice Decoding | Execute voice decoding (16Kbps).                                         |

| 06h  | None   | Voice Encoding | Execute voice encoding (24Kbps).                                         |

| 07h  | None   | Voice Decoding | Execute voice decoding (24Kbps).                                         |

| 08h  | None   | Voice Encoding | Execute voice encoding (32Kbps).                                         |

| 09h  | None   | Voice Decoding | Execute voice decoding (32Kbps).                                         |

| 0Dh  | None   | Revision Code  | Report the TL7231MD revision number in HDO0.                             |

| 0Fh  | None   | Sleep          | Go into SLEEP state. This command should be used in                      |

|      |        |                | WAIT state. If this command is used during algorithm                     |

|      |        |                | execution, TL7231MD becomes unstable.                                    |

| 10h  | None   | Mute ON        | When using internal DAC, The output voltage level of                     |

|      |        |                | AOUTL/AOUTR is GND. When using external DAC,                             |

|      |        |                | DACMUTE# becomes active. After reset, TL7231MD is                        |

|      |        |                | set to be mute on.                                                       |

| 11h  | None   | Mute OFF       | Mute is disabled.                                                        |

| 12h  | None   | Internal ADC   | Use Internal ADC. External ADC interfaces are disabled.                  |

|      |        |                | After reset, it is the default value.                                    |

| 14h  | None   | Internal DAC   | Use internal DAC. After reset, it is set to use internal DAC.            |

| 15h  | None   | External DAC   | Use external DAC. Internal DAC is disabled. The                          |

|      |        |                | waveform of I/O pin related to external DAC is controlled                |

|      |        |                | according to External DAC Format or External DAC                         |

|      |        |                | Format 2.                                                                |

| 16h  | 1byte  | External DAC   | Set the waveform of I/O pin related to external DAC. The                 |

|      |        | Format         | parameter value of External DAC Format command                           |

|      |        |                | should be as follows: {0, 0, 0, 0, 0, 1 <sup>2</sup> S, PL, PB}. For the |

|      |        |                | meaning of I <sup>2</sup> S, PL, and PB, refer to Figure 8.              |

| 17h  | None   | MSB First      | Serial Interface MSB-first mode. This is the default mode                |

|      |        |                | after reset.                                                             |

| 18h  | None   | LSB First      | Serial Interface LSB-first mode                                          |

| 19h  | 1byte  | Report Format  | The reported contents of HDO6 to HDO15 are changed                       |

|      |        |                | according to parameter of this command.                                  |

|      |        |                | Parameter Reporting Contents                                             |

|      |        |                | 0 all 00h                                                                |

|      |        |                | 1 Tone Control Information                                               |

|      |        |                | 2 MP3 Decoding Information                                               |

|      |        |                | 3 Voice Encoding/Decoding                                                |

|      |        |                | Information                                                              |

|      |        |                | 4 Equalizer Control Information                                          |

|      |        |                |                                                                          |

| 20h | 1byte | Bass Boost<br>Control<br>(MP3 Only)           | Control Bass boost. The upper nibble of the parameter controls the cutoff frequency of bass boost, and the lower nibble controls the level of bass boost. The value of upper nibble should be in the range of 0 to 6. The cutoff frequency is  25 × upper nibble + 50 (Hz).  If the values of the lower nibble is in the range of 0 to 12, the low frequency band below the cutoff frequency is boosted by 0dB ~ 18dB (1.5dB step). The other values mean no boost. For example, if the parameter value is 42h, then the cutoff frequency will be 25×4+50=150Hz, and the frequency band below 150Hz will be boosted by 3dB compared to the upper frequency band. In case of using bass boost, volume is reduced by 1.5 × n dB where n means the parameter value. The reset value is FFh(disabled). |

|-----|-------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21h | 1byte | Volume Control                                | Control volume. The parameter should have the value of range from 0 to 255. If the value is <i>n</i> , the volume is attenuated by <i>n</i> /2 dB compared to maximum volume. The reset value is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 22h | 1byte | Prescale Control                              | Control the prescaling. The parameter is a signed value and can be -128 to 127. The prescaling is done by $0.5 \times n$ dB according to parameter value $n$ . That is, $0h \sim 7Fh$ means $0dB \sim 63.5dB$ scaling, $80h \sim FFh$ means $-64dB \sim -0.5dB$ scaling. The reset value is $0dB$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 23h | 1byte | Tone Control –<br>Bass Gain<br>(MP3 Only)     | Control the Bass Gain. The parameter is a signed value and can be -128 to 127. The gain can be $0.5 \times n$ dB according to parameter value $n$ . The reset value is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24h | 1byte | Tone Control –<br>Treble Gain<br>(MP3 Only)   | Control the Treble Gain. The parameter is a signed value and can be -128 to 127. The gain can be $0.5 \times n$ dB according to parameter value $n$ . The reset value is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 25h | 1byte | Tone Control –<br>Bass Cutoff<br>(MP3 Only)   | Control the Bass Cutoff Frequency. The parameter can have the value of 0 to 255. The cutoff frequency can be $20 + 5 \times n$ Hz according to parameter value $n$ . The reset value is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 26h | 1byte | Tone Control –<br>Treble Cutoff<br>(MP3 Only) | Control the Treble Cutoff Frequency. The parameter can have the value of 0 to 255. The cutoff frequency can be $5000 + 20 \times n$ Hz according to parameter value $n$ . The reset value is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 27h | none  | Tone Control –<br>Enable<br>(MP3 Only)        | Enable the Tone Control Function. Tone Control Function is disabled when reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 28h | none  | Tone Control –<br>Disable<br>(MP3 Only)       | Disable the Tone Control Function. Tone Control Function is disabled when reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 30h | none  | MP3 CRC Bypass<br>(MP3 Only)                  | During MP3 decoding, even if the input bit stream contains the CRC field, TL7231MD doesn't check the CRC error. After reset, TL7231MD is set to check CRC error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 31h | none  | MP3 CRC Check                            | During MP3 decoding, if the input bit stream contains the CRC field, check the CRC error. If an error occurs, TL7231MD outputs 0 during the period of corresponding MP3 frame. The reset value is MP3 CRC check.                     |

|-----|-------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40h | 1byte | EQ Control –<br>Band1 Gain<br>(MP3 Only) | Control the gain of Band1( $<$ 30Hz) of 6-band equalizer. The parameter is a signed value and can be -128 to 127. The gain can be $0.5 \times n$ dB according to parameter value $n$ . The reset value is 0dB.                       |

| 41h | 1byte | EQ Control –<br>Band2 Gain<br>(MP3 Only) | Control the gain of Band2(30Hz $\sim$ 125Hz) of 6-band equalizer. The parameter is a signed value and can be - 128 to 127. The gain can be 0.5 $\times$ <i>n</i> dB according to parameter value <i>n</i> . The reset value is 0dB.  |

| 42h | 1byte | EQ Control –<br>Band3 Gain<br>(MP3 Only) | Control the gain of Band3(125Hz $\sim$ 500Hz) of 6-band equalizer. The parameter is a signed value and can be - 128 to 127. The gain can be 0.5 $\times$ <i>n</i> dB according to parameter value <i>n</i> . The reset value is 0dB. |

| 43h | 1byte | EQ Control –<br>Band4 Gain<br>(MP3 Only) | Control the gain of Band4(500Hz~2KHz) of 6-band equalizer. The parameter is a signed value and can be - 128 to 127. The gain can be $0.5 \times n$ dB according to parameter value $n$ . The reset value is 0dB.                     |

| 44h | 1byte | EQ Control –<br>Band5 Gain<br>(MP3 Only) | Control the gain of Band5(2KHz $\sim$ 8KHz) of 6-band equalizer. The parameter is a signed value and can be - 128 to 127. The gain can be 0.5 $\times$ $n$ dB according to parameter value $n$ . The reset value is 0dB.             |

| 45h | 1byte | EQ Control –<br>Band6 Gain<br>(MP3 Only) | Control the gain of Band6(>8KHz) of 6-band equalizer. The parameter is a signed value and can be -128 to 127. The gain can be 0.5 × n dB according to parameter value n. The reset value is 0dB.                                     |

| 46h | none  | EQ Control –<br>Enable<br>(MP3 Only)     | Enable the Equalizer Function. The equalizer function is disabled after reset.                                                                                                                                                       |

| 47h | none  | EQ Control –<br>Disable<br>(MP3 Only)    | Disable the Equalizer Function. The equalizer function is disabled after reset.                                                                                                                                                      |

| 8xh | None  | External DAC<br>Format2                  | Same as External DAC Format command. Parameter values are located at lower nibble of the command. The command should be the form of {1, 0, 0, 0, 0, 0, 1 <sup>2</sup> S, PL, PB}.                                                    |

Bass boost control command(20h) is another form of tone control command(23h ~28h). It is implemented by using the same filter as tone control command. Thus, if bass boost control command is received with valid parameter value, gains and cutoffs are changed as follows;

- Bass gain and cutoff frequency of tone control are changed according to the parameter value

- Treble gain is changed to 0.

- Prescaling is set to –12dB to remove clipping noise.

- Tone control is enabled.

If bass boost command is received with invalid parameter value, the gains and cutoff frequencies are not changed, and tone control is disabled. If a command related to tone control is received, only the related gain or cutoff frequency is changed, and the command has no effect on the tone control enable/disable and prescaling, and the information of bass boost which is reported through HDO13 is not changed. For the tone control enable command(27h), it just enables the tone control function, and has no effect on the gains and cutoff frequencies. Tone control disable command(28h) disable tone control function, and change the bass boost status which is reported through HDO13 to FFh(disable).

Prescaling has effect when tone control or equalizer is enabled or bass boost command is received.

Equalizer consists of 6 bands, and band1 and band6 are shelving type, band2 to band5 are peaking type. Since each band has relatively small Q value, correction matrix is automatically used to complement this small Q value whenever attenuation value is set by using EQ gain control commands(40h ~ 45h). It is not recommended that gain difference of neighbor bands exceeds 10dB.

Figure 4. HDI Status Reported through HSR4

Figure 5. Command ID reported through HDO0

Figure 6. TL7231MD Status reported through HDO1

| 7             | 6                          | 5                                                                                                                                              | 4                                                  | 3  | 2   | 1 | 0  |  |  |

|---------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----|-----|---|----|--|--|

|               | Reserve                    | ed                                                                                                                                             |                                                    | DE | MU# | ; | SF |  |  |

| Bit<br>Number | Bit<br>Mnemonic            |                                                                                                                                                | Function                                           |    |     |   |    |  |  |

| 3             | DE                         | Deem                                                                                                                                           | Deemphasis Enable:                                 |    |     |   |    |  |  |

|               |                            | When                                                                                                                                           | /hen set, deemphasis is enabled. Reset value is 0. |    |     |   |    |  |  |

| 2             | MU#                        | Mute I                                                                                                                                         | Enable:                                            |    |     |   |    |  |  |

|               |                            | When                                                                                                                                           | When cleared, mute is on. Reset value is 0.        |    |     |   |    |  |  |

| 1:0           | 1:0 FS Sampling Frequency: |                                                                                                                                                |                                                    |    |     |   |    |  |  |

|               |                            | During MP3/voice decoding, it shows the sampling frequency of bit stream. DACLRCK is set as follows:                                           |                                                    |    |     |   |    |  |  |

|               |                            | 00: 44.1KHz 01: 48KHz 10: 32KHz 11: not used During voice encoding, it shows the sampling frequency of bit stream. ADCADEN# is set as follows: |                                                    |    |     |   |    |  |  |

|               |                            |                                                                                                                                                |                                                    |    |     |   |    |  |  |

|               |                            | 00: not used 01: not used 10: not used 11: 8KHz Reset value is 00.                                                                             |                                                    |    |     |   |    |  |  |

Figure 7. I/O Status reported through HDO2

When cleared, DACSDATA has valid data between falling edges of DACBCK. When set, DACSDATA has valid data between rising edges of DACBCK. (Refer Figure 17.)

When set, external DAC is used. Reset value is 0.

When set, external ADC is used. Reset value is 0.

Polarity of DACBCK:

Reset value is 0.

External DAC Enable:

External ADC Enable:

Figure 8. I/O Status reported through HDO3

Figure 9. Volume reported through HDO4

4

1

0

PΒ

**EDAC**

**EADC**

Figure 10. Serial Interface Mode reported through HDO5

Figure 11. Count Value reported through HDO6 ~ HDO9

**Figure 12.** Frame Header reported through HDO10 when mode is 2.

| 7      | 6<br>BRI | 5 4                            | 3 2<br>SF     | PD   | PR |  |  |  |  |

|--------|----------|--------------------------------|---------------|------|----|--|--|--|--|

|        | BKI      |                                | 51            | ן אט | PK |  |  |  |  |

| Bit    | Bit      |                                | Function      | n    |    |  |  |  |  |

| Number | Mnemonic |                                | it Data Indov |      |    |  |  |  |  |

| 7:4    | BRI      | Bit Rate Index:                |               |      |    |  |  |  |  |

|        |          | 0000: Free                     |               |      |    |  |  |  |  |

|        |          | 0001: 32Kbps                   |               |      |    |  |  |  |  |

|        |          | 0010: 40Kbps<br>0011: 48Kbps   |               |      |    |  |  |  |  |

|        |          | 0100: 56Kbps                   |               |      |    |  |  |  |  |

|        |          | 0101: 64Kbps                   |               |      |    |  |  |  |  |

|        |          | 0110: 80Kbps                   |               |      |    |  |  |  |  |

|        |          | 0111: 96Kbps                   |               |      |    |  |  |  |  |

|        |          | 1000: 112Kbps                  |               |      |    |  |  |  |  |

|        |          | 1001: 128Kbps                  |               |      |    |  |  |  |  |

|        |          | 1010: 160Kbps                  |               |      |    |  |  |  |  |

|        |          | 1011: 192Kbps<br>1100: 224Kbps |               |      |    |  |  |  |  |

|        |          | 1100. 224Kbps<br>1101: 256Kbps |               |      |    |  |  |  |  |

|        |          | 1110: 320Kbps                  |               |      |    |  |  |  |  |

|        |          | 1111: Forbidden                |               |      |    |  |  |  |  |

| 3:2    | SF       | Sampling Frequency             | <i>'</i> :    |      |    |  |  |  |  |

| 0.2    |          | 00: 44.1KHz                    |               |      |    |  |  |  |  |

|        |          | 01: 48KHz                      |               |      |    |  |  |  |  |

|        |          | 10: 32KHz                      |               |      |    |  |  |  |  |

|        |          | 11: Reserved                   |               |      |    |  |  |  |  |

| 1      | PD       | Padding Bit                    |               |      |    |  |  |  |  |

|        |          | 0: No Padding Bit              |               |      |    |  |  |  |  |

|        |          | 1: One Padding Bit             |               |      |    |  |  |  |  |

| 0      | PR       | Private Bit                    |               |      |    |  |  |  |  |

| -      |          | Bit for private use.           |               |      |    |  |  |  |  |

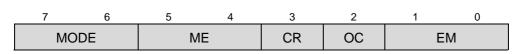

**Figure 13.** Frame Header reported through HDO11 when mode is 2.

| Bit<br>Number | Bit<br>Mnemonic | Function                                                                                                                                                                  |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6           | MODE            | Audio Channel Mode:                                                                                                                                                       |

|               |                 | 00: Stereo 01: Joint Stereo (Intensity Stereo and/or MS Stereo) 10: Dual Channel 11: Single Channel                                                                       |

| 5:4           | ME              | Joint Stereo Coding Method:                                                                                                                                               |

|               |                 | <ul><li>00: Neither Intensity Stereo nor MS Stereo</li><li>01: Only Intensity Stereo</li><li>10: Only MS Stereo</li><li>11: Both Intensity Stereo and MS Stereo</li></ul> |

| 3             | CR              | Copyright:                                                                                                                                                                |

|               |                 | 0: No Copyright 1: Copyright Protected                                                                                                                                    |

| 2             | ОС              | Original/Copy:                                                                                                                                                            |

|               |                 | 0: Copy<br>1: Original                                                                                                                                                    |

| 1:0           | EM              | Type of Deemphasis:                                                                                                                                                       |

|               |                 | 00: None 01: 50/15 microseconds 10: Reserved 11: CCITT J.17  DACDEEM of TL7231MD becomes active if deemphasis is needed without relation to deemphasis type.              |

**Figure 14.** Frame Header reported through HDO12 when mode is 2.

Figure 15. Bass Boost Information reported through HDO13 when mode is 2.

Figure 16. DAC Output Status reported through HDO14

### DAC

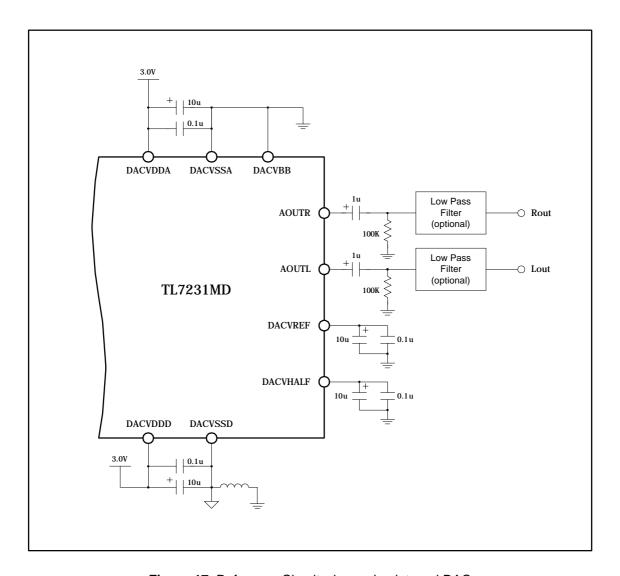

DAC of TL7231MD employs the 1-bit 4<sup>th</sup>-order sigma-delta architecture with 16-bit resolution, over-sampling of 64X. Analog post-filter with low clock sensitivity and linear phase can filter out the shaping-noise and output analog voltage with high resolution. The characteristic of Internal DAC is shown Table 7.

Table 7. Characteristics of Internal DAC

| PARAMETER                          | MIN | TYP             | MAX  | UNITS |  |  |  |

|------------------------------------|-----|-----------------|------|-------|--|--|--|

| Resolution                         |     | 16              |      | bits  |  |  |  |

| SNR                                |     | 79.7            |      | dB    |  |  |  |

| THD                                |     | 84.9            |      | dB    |  |  |  |

| SNDR                               |     | 78.5            |      | dB    |  |  |  |

| Reference Voltage Output (DACVREF) |     | 0.5×<br>DACVDDA |      | V     |  |  |  |

| Frequency Response                 |     | ± 0.1           | ±0.5 | dB    |  |  |  |

| Analog Output                      |     |                 |      |       |  |  |  |

| Voltage Range                      |     | 0.5×<br>DACVDDA |      | Vpp   |  |  |  |

| Load Impedance                     | 10K |                 |      | Ω     |  |  |  |

| Digital Filter                     |     |                 |      |       |  |  |  |

| Pass Band Ripple                   |     | ±0.0072         |      | dB    |  |  |  |

| Stop and Attenuation               |     | 62.7            |      | dB    |  |  |  |

| Pass Band                          |     | 0.45            |      | Fs    |  |  |  |

(DACVDDD/DACVDDA=3.0V, Temp=25°C, Fs=44.1KHz, Signal Freq.=20~20KHz, Cload of AOUTL/AOUTR = 10pF)

With TL7231MD, user can configure whether the internal DAC is used or not. The configuration of DAC can be achieved through HIP commands shown in Table 5. When using internal DAC, the following circuit in Figure 17 is recommended.

Figure 17. Reference Circuit when using internal DAC

### **External DAC Interfaces**

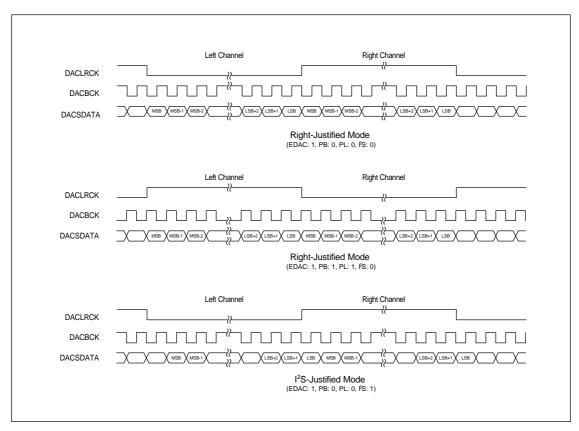

TL7231MD supports eight external interface formats. Three of them, for example, are shown in Figure 18. The interface can be configured through HIP commands. The frequency of DACBCLK is 32 times of that of DACLRCK. When voice decoding, only 32KHz of DACLRCK is used.

Figure 18. Examples of External DAC Interfaces

### **ADC**

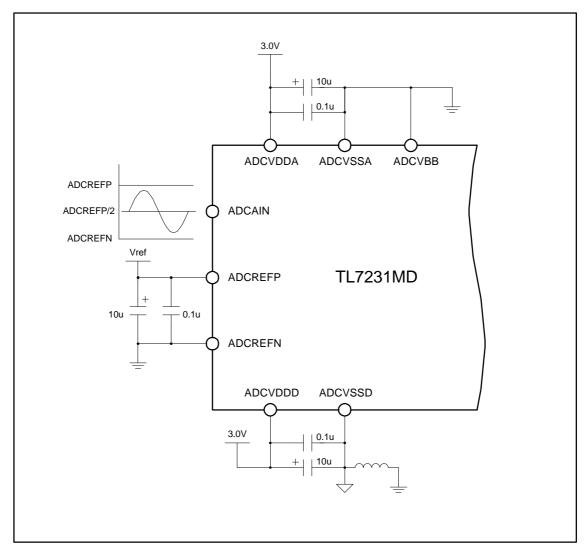

The internal ADC of TL7231MD is 12-bit resolution ADC. It is recycling type ADC with sample-and-hold function. The analog input ADCAIN should be single-ended type with the range from ADCREFP to ADCREFN. This ADCAIN voltage follows reference voltage range fundamentally. So, if user wants to alter the input range, the voltage value of ADCREFP should be changed. But ADCREFP should be greater than 2.0V. The characteristic of internal ADC is shown Table 8.

Table 8. Characteristics of Internal ADC

| PARAMETER | MIN | TYP  | MAX | UNITS |

|-----------|-----|------|-----|-------|

| THD       |     | 74.3 |     | dB    |

| SNR       |     | 64.9 |     | dB    |

| SNDR      |     | 64.4 |     | dB    |

(ADCVDDD/ADCVDDA=3.0V, ADCAIN=8KHz)

Figure 19. Reference Circuit when using internal ADC

With TL7231MD, the following circuit in Figure 19 is recommended to use internal ADC.

## **Voice Record/Playback Function**

TL7231MD records voice data from ADC in 8kHz sampling rate. There are three compression modes according to bit rates of compressed data: high quality (32Kbps), medium quality (24Kbps) and low quality (16Kbps). In high quality mode, relatively large bits are allocated for compressed data to achieve high quality of the sound. In low quality mode, smaller bits are allocated to record much more samples in the same size of storage media. Medium quality mode gives tradeoff between high and low quality modes. Compressed codes are byte-aligned and transmitted to host MCU through the serial port.

In playback the codes are uncompressed to PCM samples, with the compression mode in recording, and then oversampled to 32 kHz and output to DAC. Compressed codes are transmitted from host MCU through the serial interface.

Table 9 is the summary of the relation between compression modes and code size.

Table 9. Summary of Three Voice Compression Modes

| COMPRESSION MODES       | CODE LENGTH<br>(BIT) | RECORDING TIME FOR 32MB STORAGE MEDIA |

|-------------------------|----------------------|---------------------------------------|

| High Quality (32Kbps)   | 4                    | 140 min.                              |

| Medium Quality (24Kbps) | 3                    | 186 min.                              |

| Low Quality (16Kbps)    | 2                    | 280 min.                              |

## **Lower Power Operation**

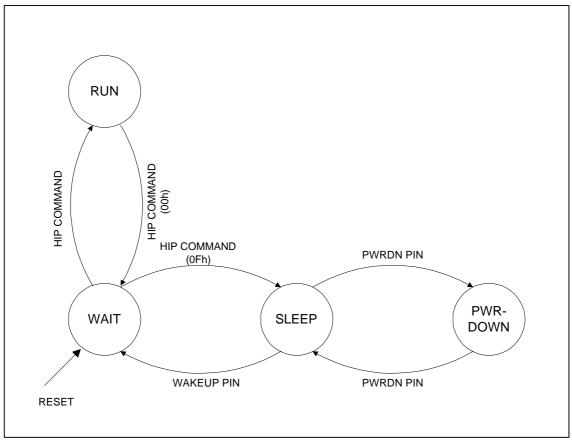

TL7231MD has low-power feature that makes the processor get into very low-power dormant states through hardware or software control. The power saving scheme is explained with the state diagram of TL7231MD shown in Figure 20.

#### RUN

In this state, TL7231MD decodes MP3 or compressed voice bit stream, or encodes voice signal. Also in this state it can process other HIP commands such as 20h and 21h. HIP command 01h, 04h through 09h, and 0Fh should not be used in this state. TL7231MD consumes normal power at this state, It processes all internal functions and drives external pads. It can transit to WAIT state with HIP command 00h. When there is no job left or it waits available data, power consumption is reduced as that of WAIT state.

### WAIT

When RESET signal becomes active, TL7231MD goes into WAIT state. There it can transit to RUN, or SLEEP state. When TL7231MD is in this state, it is ready to receive any HIP commands from host. It can go into RUN state when it receives HIP commands such as 01h, 04h though 09h. Also it can process other HIP commands such as volume control (21h) etc. in this state. TL7231MD goes into this state through HIP command 00h from RUN state. When TL7231MD is in this state, only peripheral interface block consumes power. That is, internally generated peripheral clock is active but clock for the DSP core logic is not. When it receives HIP command 0Fh, it goes into SLEEP state in which more power is saved.

### **SLEEP**

In SLEEP state, only internal analog blocks such as PLL, ADC and DAC of TL7231MD consume power. In this state, internal ADC and DAC are disabled. But PLL consumes normal operation power. In this state, TL7231MD can transit to PWRDOWN state when external PWRDN pin becomes active. Active WAKEUP signal changes its state from SLEEP to WAIT.

### **PWRDOWN**

When TL7231MD is in SLEEP state and PWRDN signal becomes active, it transits to PWRDOWN. To make TL7231MD stay in this state, the external PWRDN signal keep its active state. When the PWRDN signal becomes inactive, TL7231MD exits from this PWRDOWN state, and then goes into SLEEP state. When it changes its state from PWRDOWN to SLEEP, this state should not be changed during minimum 150µs until internal PLL is stabilized. TL7231MD consumes the minimum power at this state because all internal logic blocks and analog blocks are power-downed.

Figure 20. Decoder States and Power Management

## **ELECTRICAL SPECIFICATIONS**

## **ABSOLUTE MAXIMUM RATINGS (See Notes)†**

| Symbol           | Parameter           | Rating      | Unit |

|------------------|---------------------|-------------|------|

| $V_{DD}$         | DC Supply Voltage   | -0.3 to 3.8 | V    |

| $V_{IN}$         | DC Input Voltage    | -0.3 to 5.5 | V    |

| I <sub>IN</sub>  | DC Input Current    | ±10         | mA   |

| T <sub>STG</sub> | Storage Temperature | -40 to 125  | °C   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "DC ELECTRICAL CHARACTERISTICS" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

not sustained during normal device operation.

## DC ELECTRICAL CHARACTERISTICS (Note3)†

| Symbol             | Parameter                                                 | MIN  | TYP | MAX                  | UNIT |

|--------------------|-----------------------------------------------------------|------|-----|----------------------|------|

| $V_{DD}$           | Supply voltage                                            | 2.7  | 3.0 | 3.3                  | V    |

| V <sub>ss</sub>    | Supply voltage                                            |      | 0   |                      | V    |

| $V_{IH}$           | High level input voltage                                  | 1.8  |     | V <sub>DD</sub> +0.3 | V    |

| $V_{IL}$           | Low level input voltage                                   | -0.3 |     | 0.6                  | V    |

| $V_{OH}$           | High level output voltage                                 | 2    |     |                      | V    |

| $V_{OL}$           | Low level output voltage                                  |      |     | 0.4                  | V    |

| I <sub>IH</sub>    | High level input leakage current without internal pull-up | -10  |     | +10                  | μΑ   |

| I <sub>IL</sub>    | Low level input leakage current without internal pull-up  | -10  |     | +10                  | μΑ   |

| $I_{RN}$           | I <sub>RN</sub> Supply current in RUN state               |      |     |                      | mΑ   |

| $I_{WT}$           | Supply current in WAIT state                              | 26   |     |                      | mΑ   |

| I <sub>SL</sub>    | Supply current in SLEEP                                   | 12   |     |                      | mΑ   |

| I <sub>PD</sub>    | Supply current in PWRDOWN state                           | 250  |     |                      | μΑ   |

| $C_{IN}$           | Input capacitance                                         |      |     | 4                    | pF   |

| C <sub>OUT</sub>   | Output capacitance                                        |      |     | 4                    | pF   |

| $T_A$              | Air temperature                                           | -40  |     | 85                   | °C   |

| V <sub>CPUXI</sub> | High level input voltage for CPUXI                        | 2.5  | **  | V <sub>DD</sub> +0.3 | V    |

<sup>†</sup> For TL7231MD, all typical values are at  $V_{DD}$  = 3.0 V,  $T_A$  (air temperature) = 25°C.

NOTE 3: All voltage values are with respect to Vss. All input and output voltage levels are TTL-compatible. CLKIN can be driven by CMOS clock.

NOTICE: This document contains information on products in the sampling and initial production phases of development. The specifications are subject to change without notice.

## **AC ELECTRICAL CHARACTERISTICS**

### **AC Test Condition**

| Parameter                 | Value |

|---------------------------|-------|

| Temperature               | 85°C  |

| Supply Voltage            | 3.0V  |

| Input Rise and Fall Times | 2ns   |

| Output Load               | 10pF  |

## **Serial port**

The following table defines the timing parameters for the serial port pins. The numbers shown in Figure 21 correspond to each number in the first column of the table.

| NO. | Symbol           | Description                                                           | MIN   | MAX   | Unit |

|-----|------------------|-----------------------------------------------------------------------|-------|-------|------|

| 1   | T <sub>CC</sub>  | Cycle time of CLKXRM                                                  | 144.7 |       | ns   |

| 2   | T <sub>D</sub>   | Delay time, CLKXRM to DXRM valid                                      | 42.2  | 78.4  | ns   |

| 3   | T <sub>SU</sub>  | Setup time, DXRM before CLKXRM low                                    | 1.9   |       | ns   |

| 4   | T <sub>H</sub>   | Hold time, DXRM from CLKXRM low                                       | 1.2   |       | ns   |

| 5   | T <sub>REQ</sub> | Request check time, falling edge of CLKXRM to falling edge of REQSTRM | 295.2 | 331.3 | ns   |

Figure 21. Timing for Serial Port in case of LSB-First Mode

### **Host interface Port**

The following table defines the timing parameters for the Host Interface Port I/O pins. The numbers shown in Figure 22 correspond to each number in the first column of the table.

| NO. | Symbol            | Description                                   | MIN  | MAX | Unit |

|-----|-------------------|-----------------------------------------------|------|-----|------|

| 6   | T <sub>HAW</sub>  | HALE pulse width                              | 2.0  |     | ns   |

| 7   | T <sub>HDSU</sub> | Setup time, HD address setup before HALE low  | 2.0  |     | ns   |

| 8   | T <sub>HDH</sub>  | Hold time, HD address hold after HALE low     | 0.8  |     | ns   |

| 9   | T <sub>HAS</sub>  | Start of write or read after HALE low         | 0.0  |     | ns   |

| 10  | T <sub>HDSU</sub> | Setup time, HD data setup before end of write | 0.7  |     | ns   |

| 11  | T <sub>HDH</sub>  | Hold time, HD data hold after end of write    | 2.2  |     | ns   |

| 12  | T <sub>HRW</sub>  | Read or write pulse width                     | 36.2 |     | ns   |

| 13  | T <sub>HDE</sub>  | HD data enabled after start of read           | 7.8  |     | ns   |

| 14  | T <sub>HDD</sub>  | HD data valid after start of read             | 7.9  |     | ns   |

| 15  | T <sub>HRDH</sub> | HD data hold after end of read                | 3.7  | 7.8 | ns   |

| 16  | T <sub>HRDD</sub> | HD data disabled after end of read            | 4.2  | 7.9 | ns   |

Figure 22. Timing for Host Interface Port pins

## **PACKAGE DIMENSION**

# 100-TQFP-1414

The reproduction of this datasheet is NOT allowed without approval of SEC.

All information and data contained in this datasheet are subject to change without notice. This publication supersedes and replaces all information previously supplied. SEC has no responsibility to the consequence of using the patents described in this document.

©1999 SAMSUNG Electronics Co., - All Rights Reserved